# SOFTWARE DESIGN DOCUMENT

### for the

# DETECTOR CONTROL ELECTRONICS (DCE) FLIGHT SOFTWARE

for the

# **COSMIC ORIGINS SPECTROGRAPH (COS)**

Contract No. NAS5-98043 CDRL No. DM-03

Prepared for:

Goddard Space Flight Center Greenbelt, MD

Prepared by:

Experimental Astrophysics Group, Space Sciences Laboratory University of California, Berkeley

#### COS-UCB-009

Prepared By:

**Reviewed By:**

Daniel Blackman FUV Detector Software Lead Geoff Gaines FUV Detector Systems Engineer

Robert Lampereur COS Flight Software Engineer

Allison Elliott COS Flight Software Engineer

Approved By:

Dr. Kenneth Brownsberger HST-COS Software Scientist University of Colorado, Boulder Grant Blue BATC COS Software Manager

Date

# **Revision Record**

| Rev | Date | Reason for Revision | Project Released |

|-----|------|---------------------|------------------|

|     |      |                     |                  |

| -   |      | Original Issue      |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

|     |      |                     |                  |

# **Table of Contents**

| 1 | SCOP     | Ε                                                   | 6  |

|---|----------|-----------------------------------------------------|----|

|   | 1.1 Iden | VTIFICATION                                         | 6  |

|   | 1.2 Sys  | TEM OVERVIEW                                        | 6  |

|   |          | CUMENT OVERVIEW                                     |    |

| 2 | APPL     | ICABLE DOCUMENTS                                    | 9  |

|   | 2.1 Rel  | ATIONSHIP TO OTHER DOCUMENTS                        | 9  |

|   | 2.2 Ref  | ERENCED DOCUMENTS                                   | 9  |

|   | 2.2.1    | COS Documentation                                   | 9  |

|   | 2.2.2    | Commercial Off-the-Shelf Documentation              | 9  |

| 3 | TOP-I    | LEVEL DESIGN                                        |    |

|   | 3.1 Fun  | CTIONAL OVERVIEW                                    |    |

|   |          | IPUTER SOFTWARE COMPONENTS (CSCs)                   |    |

|   | 3.2.1    | Resets and Initialization CSC                       |    |

|   | 3.2.2    | Command Reception and Processing CSC                |    |

|   | 3.2.3    | Housekeeping Collection and Reporting CSC           |    |

|   | 3.2.4    | Current Limit Checking CSC                          |    |

|   | 3.2.5    | Global Rate Protection CSC                          |    |

|   | 3.2.6    | Detector Control CSC                                |    |

|   | 3.2.7    | Door Control CSC                                    |    |

|   | 3.2.8    | Background Monitoring CSC                           |    |

|   | 3.2.9    | Support Functions CSC                               |    |

|   | 3.2.10   | Time Management CSC                                 |    |

|   | 3.3 Con  | ITROL FLOW                                          |    |

|   | 3.4 DAT  | TA FLOW                                             |    |

|   | 3.5 Haf  | DWARE INTERFACES                                    |    |

|   | 3.5.1    | Interfaces Between the CS and DCE FSW               |    |

|   | 3.5.2    | Interfaces Between the DCE FSW and the FUV Hardware | 24 |

|   | 3.6 Ope  | RATING MODES                                        |    |

|   | 3.6.1    | Boot Mode                                           | 27 |

|   | 3.6.2    | Operate Mode                                        | 27 |

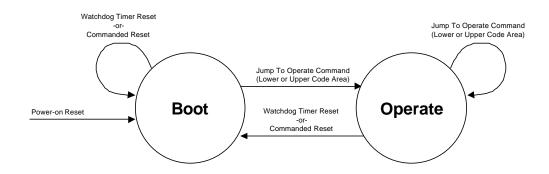

|   | 3.6.3    | Mode Transitions                                    |    |

| 4 | DETA     | ILED DESIGN                                         |    |

|   | 4.1 Des  | ign Approach                                        |    |

|   | 4.1.1    | Reuse from Previous Missions                        |    |

|   | 4.1.2    | Memory Utilization and Commanding                   |    |

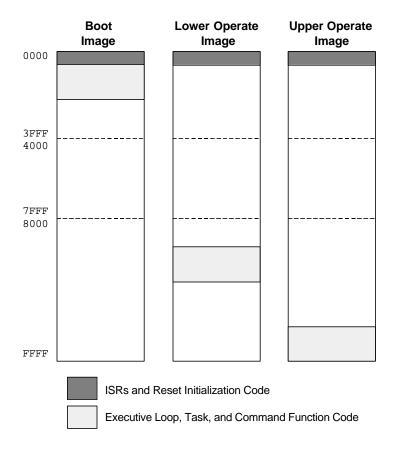

|   | 4.1.3    | Boot and Operate Software Designs                   |    |

|   | 4.2 Sof  | TWARE ARCHITECTURE                                  |    |

|   | 4.2.1    | Operating System                                    |    |

|   | 4.2.2    | Resets and Initialization                           |    |

| 4.2.3    | Executive Loop                    | 37 |

|----------|-----------------------------------|----|

|          |                                   |    |

| 4.2.4    | Interrupt Service Routines        |    |

| 4.2.5    | Tasks                             |    |

| 4.2.6    | Inspect and Change Task           |    |

| 4.2.7    | Miscellaneous Functions           |    |

| 4.2.8    | DCE Commands                      |    |

| 4.2.9    | Timing Considerations             |    |

| 4.3 INTE | ernal Hardware Interfaces         |    |

| 4.3.1    | 8051 Ports                        |    |

| 4.3.2    | Memory Mapped I/O                 |    |

| 4.4 Pro  | CESSING HARDWARE                  |    |

| 4.4.1    | 8051 Micro-controller             |    |

| 4.4.2    | External Memory                   |    |

| 4.4.3    | Hardware Environment              |    |

| 5 DEVE   | LOPMENT ENVIRONMENT               |    |

| 5.1 Pro  | GRAMMING LANGUAGE                 |    |

| 5.2 Sof  | TWARE TOOLS                       |    |

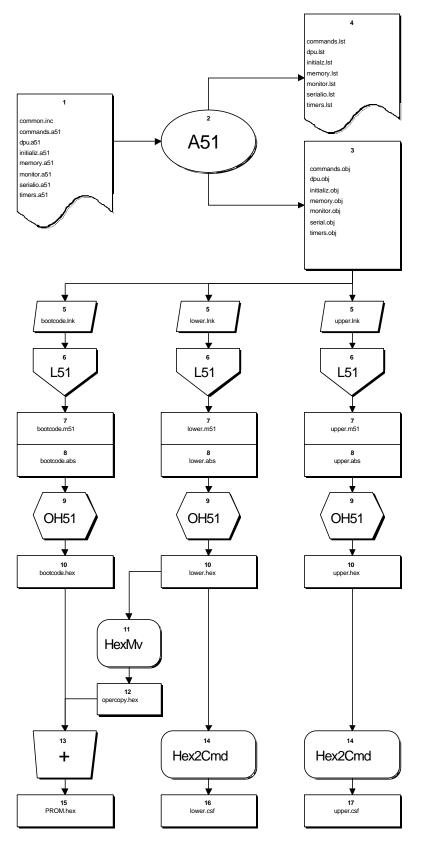

| 5.2.1    | DCE Flight Software Build Process |    |

| 5.2.2    | Interface to SI Memory Manager    |    |

| 6 DESIG  | GN REQUIREMENTS TRACEABILITY      |    |

| 7 ACRO   | DNYMS AND TERMS                   |    |

# Table of Figures

| COS BLOCK DIAGRAM                             | 8                                 |

|-----------------------------------------------|-----------------------------------|

| SYSTEM LEVEL CONTROL FLOW DIAGRAM             | 19                                |

| CONTEXT LEVEL DATA FLOW DIAGRAM               | 21                                |

| FUV DETECTOR FUNCTIONAL BLOCK DIAGRAM         | 23                                |

| DCE FLIGHT SOFTWARE OPERATING MODES           | 28                                |

| CODE IMAGE LOCATION IN DCE MEMORY             | 30                                |

| DCE RESETS                                    | 33                                |

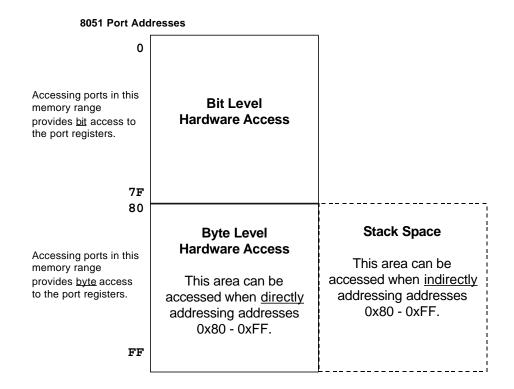

| PORT MAPPING OF INTERNAL 8051 MEMORY          | 90                                |

| 8051 INTERNAL REGISTERS PROVIDING BYTE ACCESS | 91                                |

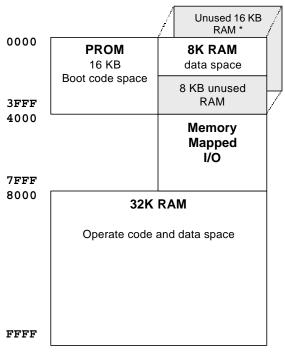

| DCE MEMORY MAP                                | 96                                |

| DCE 32K RAM MEMORY ALLOCATION                 | 96                                |

| DCE FSW Build Process                         | 99                                |

|                                               | SYSTEM LEVEL CONTROL FLOW DIAGRAM |

# 1 SCOPE

### 1.1 Identification

This Software Design Document (SDD) establishes the software design for the Far UltraViolet (FUV) Detector Control Electronics (DCE) Flight Software (FSW) Computer Software Configuration Item (CSCI) for the Cosmic Origins Spectrograph (COS) instrument. The COS instrument is to be installed into the Hubble Space Telescope (HST) as part of a future HST Servicing Mission. The developer of the FUV Detector Subsystem, which includes the DCE FSW, is the Experimental Astrophysics Group (EAG) at the Space Science Laboratory, University of California, Berkeley.

This document has been prepared in accordance with the requirements of contract NAS5-98043, between Goddard Space Flight Center (GSFC) Code 442, Greenbelt, Maryland, and University of Colorado/Center for Astrophysics and Space Astronomy (CU/CASA), Boulder, Colorado. It is written in accordance with SCM-1050, HST COS Data Requirements Document, Part DM-03.

## 1.2 System Overview

COS is a fourth generation axial replacement instrument for the Hubble Space Telescope. The capabilities of COS allow astronomers to pursue programs of scientific interest that are not feasible with previous generation HST instruments.

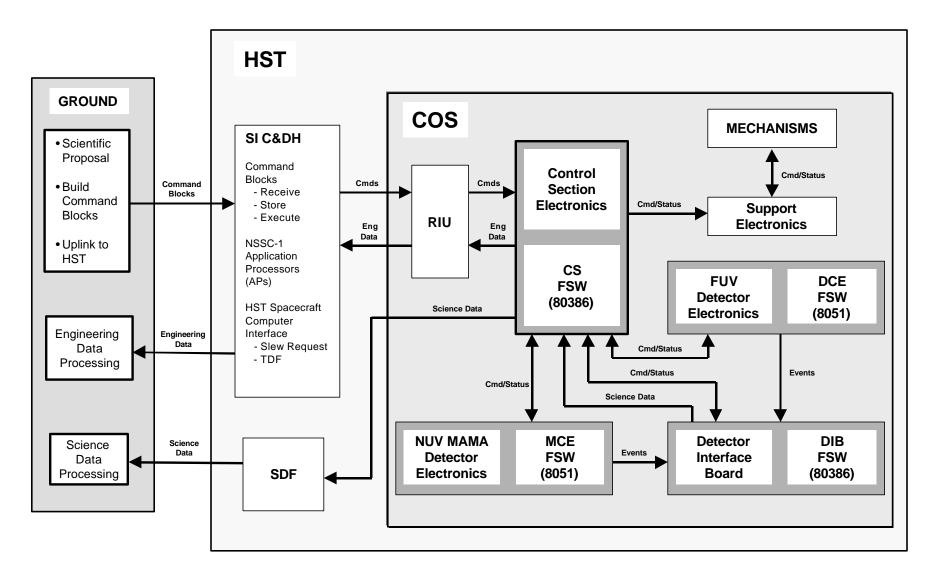

Figure 1.2-1 is a top-level block diagram showing the flow of information to and from the COS instrument. As shown in the figure, scientific proposals are converted into the appropriate command blocks that are uplinked to the HST. Commands are received and distributed by the Science Instrument Command and Data Handling System (SI C&DH) which is the interface between the HST spacecraft and the HST science instruments. The SI C&DH sends the COS specific commands to the COS instrument via the Remote Interface Unit (RIU). The Control Section (CS) is responsible for accepting and processing the macro commands (or macros) forwarded by the RIU. Some macros require the CS to communicate with the DCE. Upon receipt of a macro command, the CS validates it and sends the appropriate sub-system level commands to the DCE.

Within the FUV Detector Subsystem, the DCE FSW provides the FUV detector with the computational, interface, and memory resources necessary for performing FUV detector control activities. Commands from the CS are accepted and processed by the DCE FSW. The DCE FSW outputs engineering telemetry data in the form of housekeeping packets. The DCE FSW controls the FUV detector hardware that generates science data, however, it sees only counts and not location information for each photon event. Science data does not pass through the DCE FSW, but rather is output from FUV detector hardware to the Detector Interface Board (DIB) for processing by the DIB flight software.

### 1.3 Document Overview

This Software Design Document describes how the requirements that have been allocated to the COS DCE FSW are satisfied by the design. The organization of this document is outlined below with a description of each major section.

- Section 1 defines the scope of this document and introduces the FUV Detector Subsystem and DCE FSW.

- Section 2 lists documents that have been directly or indirectly referenced by this document.

- Section 3 presents the top-level design of the DCE FSW.

- Section 4 presents the detailed design of the DCE FSW.

- Section 5 presents DCE FSW development environment.

- Section 6 describes the DCE hardware and software operating environments.

• Section 7 - contains a glossary of document acronyms and terms.

Figure 1.2-1. COS Block Diagram

# 2 APPLICABLE DOCUMENTS

# 2.1 Relationship To Other Documents

This Software Design Document describes both the top-level and detailed design of the COS DCE flight software. The design indicates how the system level requirements assigned to the DCE FSW are being fulfilled. Software requirements are detailed in the DCE FSW Requirements Document (COS-UCB-004). Requirements traceability is documented in matrix format in the FUV Software Test Plan (COS-UCB-008). Many details of FUV detector operations along with the command and housekeeping interface to the MEB are described in the FUV ICD (COS-UCB-001) and the COS Flight Software User's Guide (DM-03).

# 2.2 Referenced Documents

These documents provide additional details concerning the design and implementation of features required of the DCE FSW.

# 2.2.1 COS Documentation

- Interface Control Document, FUV Detector Subsystem, COS-UCB-001

- Configuration Management Document, FUV Detector Subsystem, COS-UCB-003

- DCE Flight Software Requirements Document, COS-UCB-004

- FUV Detector Configuration Management Plan, COS-UCB-005

- FUV Detector Software Test Plan, COS-UCB-008

- FUV Detector Software Test Procedures

- COS Control Section Flight Software Requirements Document, DM-03

- FUSE DPU Source Code (source code is referenced since FUSE has no Software Design Document)

- DCE Hardware/Software Interface Document

- COS Flight Software User's Manual, DM-03

# 2.2.2 Commercial Off-the-Shelf Documentation

- MCS 51 Micro-controller Family User's Manual, Order Number 272383-002, Intel, Feb '94

- Archimedes MCS-51 Macro Assembler, Version 5.02, Archimedes Software Inc.

- Archimedes L51 Linker/Locator, Version 3.52, Archimedes Software Inc.

- Archimedes MCS-51 Object-to-Hex File Converter, Version 2.1, Archimedes Software Inc.

# 3 TOP-LEVEL DESIGN

The top-level design portion of this document addresses the overall functionality of the DCE FSW. It shows how the system requirements are fulfilled by the overall flight software design.

The top-level design is presented from of an operational perspective and attempts to do the following:

- provide high-level descriptions of the internal processes of the DCE FSW and how those processes map to the system requirements

- identify flow of control and the events that can affect the processing of data

- examine the data flowing in and out of the system

- describe the hardware interfaces external to the DCE FSW

- address the flight software operating modes

The top-level design is broken down into several sections. The first section gives a functional overview of the DCE FSW. It describes each Computer Software Component (CSC) of the software and explains how that component fulfills certain system requirements. This section comes first since it provides an overview of what the DCE FSW does, and not how it does it.

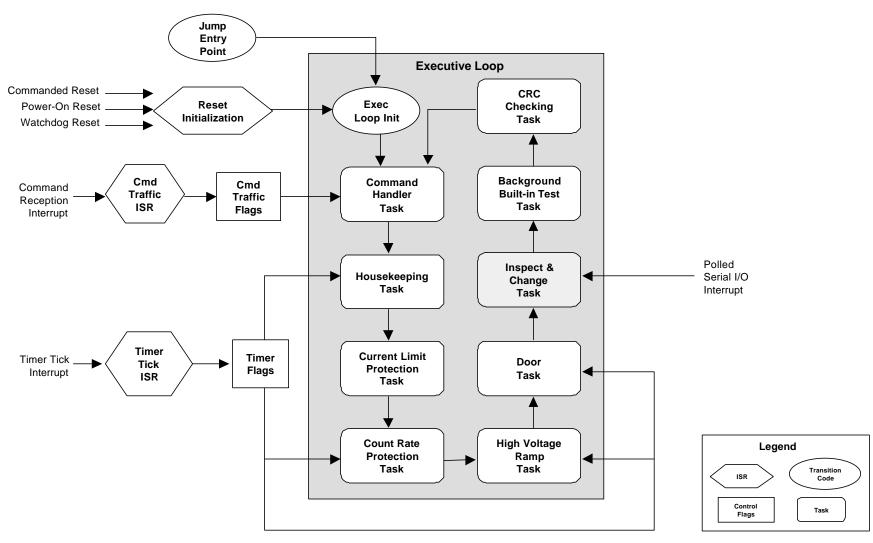

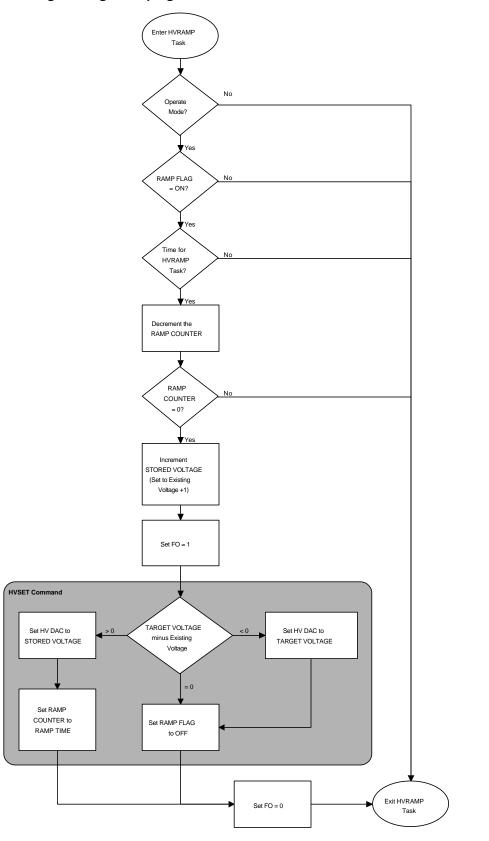

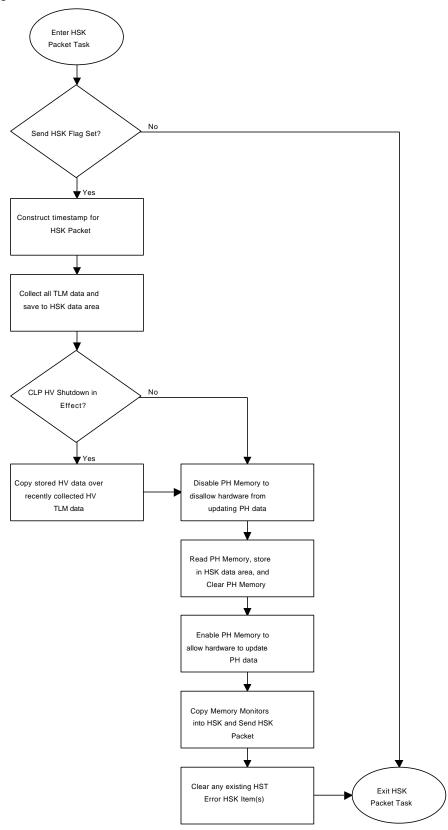

The control flow section shows how the software components are combined to form the DCE FSW. This section shows the flow of control through the system, and how processing logic is affected by the various events that occur in the system. The System Level Control Flow Diagram (Figure 3.3-1) is included to graphically show how the DCE FSW works.

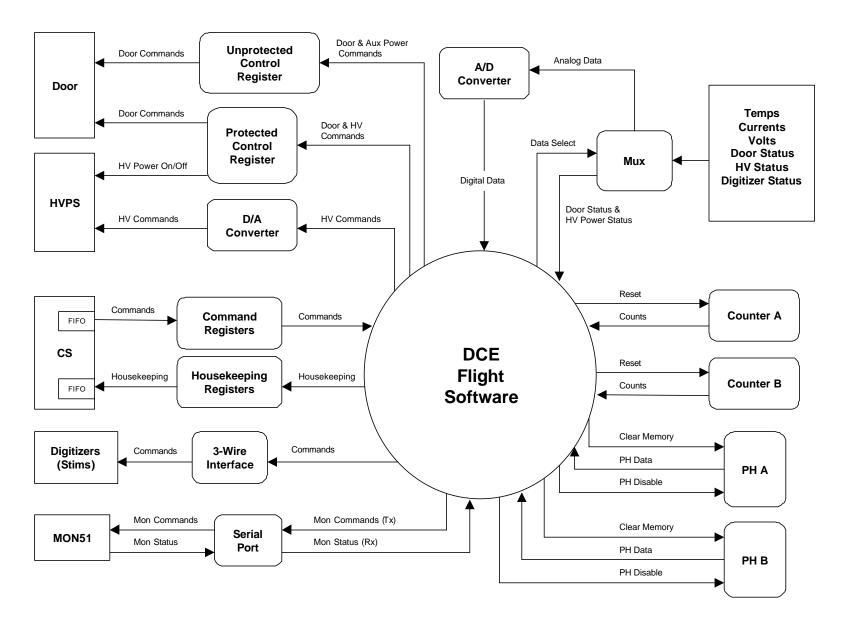

The data flow section shows how data flows in and out of the DCE FSW. This section is only concerned with data that enters and leaves the flight software. The Context Level Data Flow Diagram (Figure 3.4-1) is included to graphically show the system-level data flows.

The hardware interfaces section describes the interfaces that are external to the DCE flight software. The interfaces are dealt with at a high-level. The intent is to describe the type of hardware control and status that is provided by the DCE FSW. Each interface described in this section is represented on the Context Level Data Flow Diagram (Figure 3.4-1).

The last section looks at the DCE FSW operating modes. This section describes the various operating modes and how the user transitions from one mode to another.

### 3.1 Functional Overview

The FUV Detector Control Electronics (DCE) is the main control and coordination center for the FUV Detector Subsystem. It provides the FUV detector with the computational, interface, and memory resources necessary for performing FUV detector control operations. The DCE flight software resides in the DCE and provides the control and status capabilities of the FUV detector.

When power is applied to the FUV Detector Subsystem, the DCE FSW begins executing. The FSW is responsible for initializing its own operating environment and putting the DCE hardware in a known configuration. After the FSW has initialized, it is ready to accept commands from and provide status to the Control Section.

The DCE FSW accepts and validates incoming command packets sent from the CS. The command packets allow the CS to control and configure the FUV detector. The DCE FSW supports commands that configure the digitizers, set voltage limits, ramp the high-voltage, move the door mechanism, and generally support FUV detector operations.

The DCE FSW returns housekeeping data to the CS. Housekeeping provides insight into the state of the FUV detector. The FSW collects engineering data and formats it for output to the CS via the housekeeping interface.

Engineering data comes in many forms including temperatures, voltages, currents and other sensor data that are converted to a digital format.

The DCE FSW provides other necessary functions beyond command and status. It performs internal limit checking of critical detector parameters, reports the rate at which detector events are occurring to protect the FUV detector from an overlight condition, and performs various background checks to ensure the integrity of the operating environment.

Though the DCE FSW controls the FUV detector hardware, it does not process the science data generated by the FUV hardware. The FSW sees only counts and not coordinate information for each photon event. Science data does not pass through the DCE FSW, but rather is output from the FUV detector to the Detector Interface Board (DIB) for processing by the DIB flight software.

# 3.2 Computer Software Components (CSCs)

This section examines the functionality of the DCE flight software from a high level. It looks at the Computer Software Components (CSCs) that make up the DCE FSW. A CSC is a logical grouping of software that performs a common function. When viewed at the detailed level, a CSC consists of one or more software units. A software unit is a function, task or interrupt service routine. In this section only the high level functionality is addressed. The detailed design section of this document looks at the software units that comprise the various CSCs.

This section introduces the various CSCs that comprise the DCE FSW. It shows how the CSCI level requirements map to the CSCs. This section does not call out specific requirements that are being fulfilled, but rather addresses requirements in logical groupings. For a complete mapping of the DCE FSW requirements to the flight software design, see section 6 of this document, *Design Requirements Traceability*. For a mapping of DCE FSW requirements to software tests, see the FUV Detector Software Test Plan (COS-UCB-008).

The requirements allocated to the DCE FSW CSCI as stated in the DCE Flight Software Requirements Document (COS-UCB-004) are grouped as follows:

- DCE FSW Initialization

- Command Reception and Processing

- Detector Operations and Protection

- Door Control and Protection

- Memory Management

The DCE flight software must provide certain functionality based on the requirements allocated to the DCE FSW CSCI. The following is a list of the CSCs that comprise the DCE FSW CSCI. One or more of the CSCs may satisfy the requirement groups listed above.

- *Resets and Initialization CSC* Initializes the DCE and FUV detector electronics along with the DCE FSW operating environment. This CSC satisfies *DCE FSW Initialization* requirements.

- *Command Reception and Processing CSC* Accepts and processes command packets and memory upload data from the CS. This CSC satisfies *Command Reception and Processing* requirements.

- *Housekeeping Collection and Reporting CSC* Provides status of the FUV Detector Subsystem to the CS via housekeeping data. This includes the logging of all diagnostic and error conditions detected by the DCE FSW. This CSC satisfies *Command Reception and Processing* and *Memory Management* requirements.

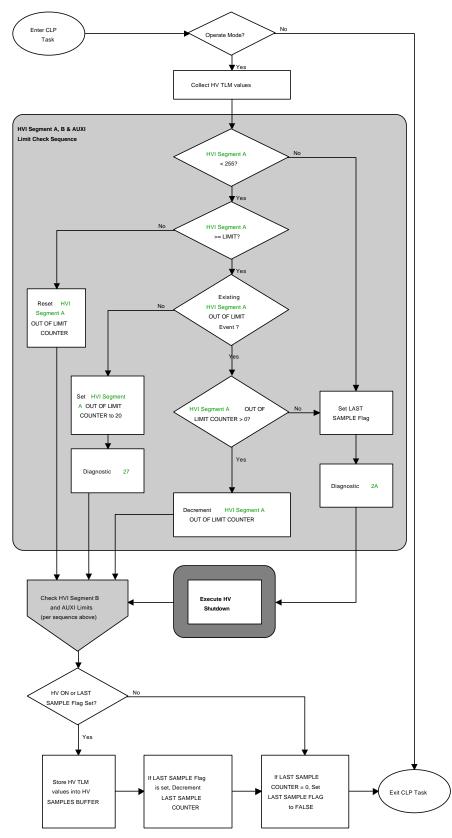

- *Current Limit Checking CSC* Monitors critical detector hardware limits and maintains the detector in a safe configuration. This CSC satisfies *Detector Operations and Protection* requirements.

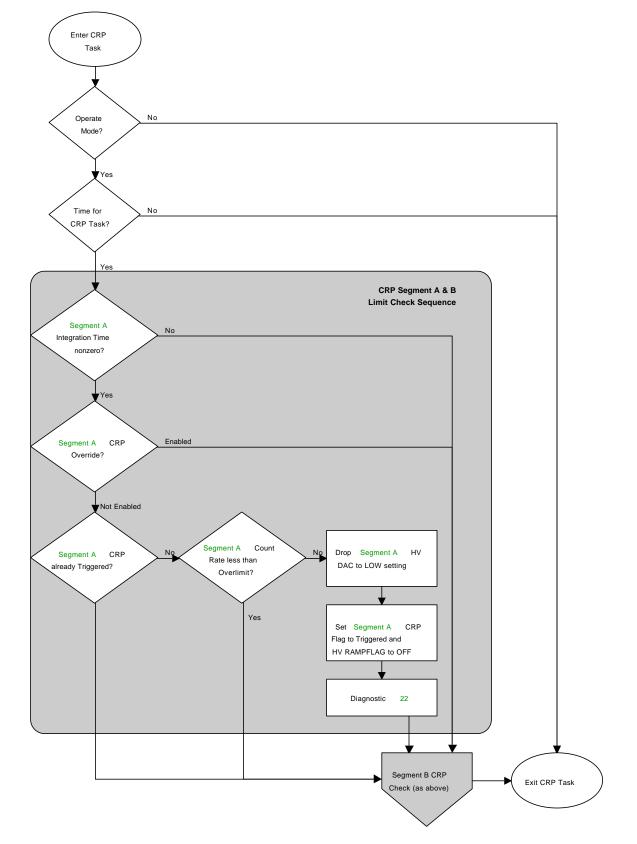

- *Global Rate Protection CSC* Provides count rate protection of the detector to protect it from potential overlight conditions. This CSC satisfies *Detector Operations and Protection* requirements.

- *Detector Control CSC* Configures and controls the FUV detector hardware. This includes the control and monitor of high-voltage ramping of the FUV detector. This CSC satisfies *Detector Operations and Protection* requirements.

- *Door Control CSC* Provides control and status of the FUV door mechanism. This CSC satisfies *Door Control and Protection* requirements.

- *Background Monitoring CSC* Performs internal tests to ensure the integrity of the DCE FSW operating environment. This CSC satisfies *Memory Management* requirements.

- Support Functions CSC Provides a variety of commands that support FUV detector operations including the cyclic-redundancy checks, memory loads, and memory copies among other capabilities. This CSC satisfies DCE FSW Initialization, Command Reception and Processing, and Memory Management requirements.

- *Time Management CSC* Allows the DCE FSW to perform certain functions on a periodic basis. This CSC satisfies *Command Reception and Processing*, *Detector Operations and Protection*, and *Door Operations and Protection* requirements.

The following sections address each CSC individually. They provide a functional description of the software component.

# 3.2.1 Resets and Initialization CSC

This CSC is responsible for initializing the DCE and FUV detector electronics along with the DCE FSW operating environment. It consists of the initialization software that is executed in response to any system reset. The DCE FSW implements a reset and initialization scheme that ensures the FSW is in a known configuration after any type of reset occurs.

Resets come in two flavors: unexpected resets and expected resets. An unexpected reset occurs due to a single event upset (SEU) or some other anomalous condition. An SEU occurs when a bit in memory gets flipped causing the software to execute out of an unexpected area of memory. Expected resets occur as part of normal detector operations. They include the power-on reset that occurs when power is applied to the DCE, and commanded resets that occur when a reset command is issued to the DCE or when the CS toggles the DCE hardware reset line.

All resets, whether unexpected and expected, are classified as one of three types:

- *Power-On Reset*: Only occurs as a result of power being applied to the DCE hardware.

- *Watchdog Timer Reset*: Occurs as a result of an SEU or the CS *not* sending a command to the DCE at least once every 10 seconds.

- *Commanded Reset*: Occurs when either the DCE is commanded by the CS to reset itself, or when the CS toggles the DCE hardware reset line. Commanded resets come in several forms and are described in detail in section 4.2.2 of the detailed design.

The reset and initialization software ensures that evidence of the state of the DCE FSW remains intact when an unexpected reset occurs. This allows ground personnel to analyze the contents of DCE memory to determine the nature of the problem. Information left over in DCE memory after an unexpected reset can be very helpful in reconstructing and understanding what happened.

The detailed description of how the DCE FSW handles each type of reset is covered in the detailed design section of this document.

# 3.2.2 Command Reception and Processing CSC

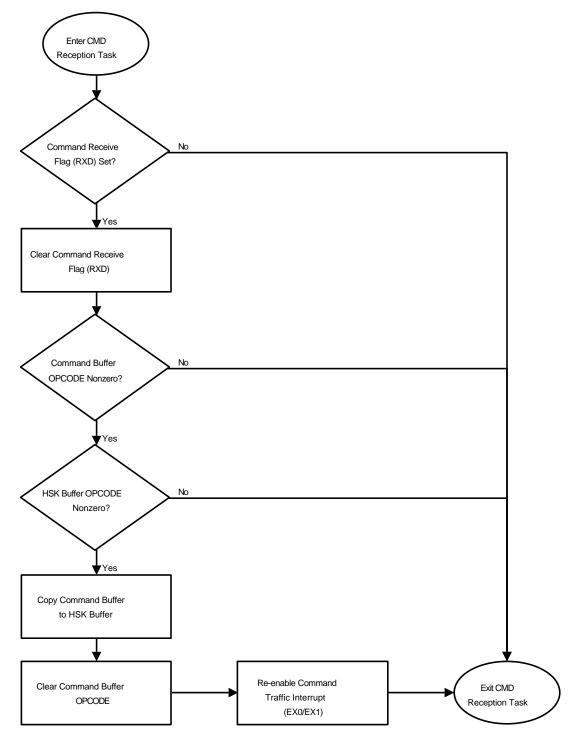

Activities performed by the FUV Detector Subsystem in support of science observations and detector maintenance are initiated and controlled through the use of command information sent to the DCE FSW from the CS. The DCE FSW provides the ability to accept the incoming command packets from the CS and perform the required actions indicated by the command op-code.

The DCE FSW implements a commanding structure that consists of command packets that are made up of 32-bit command words. A DCE command packet consists of multiple command words with each command word processed individually by the DCE FSW. After all of the command words associated with a command packet are received, the DCE FSW takes the appropriate action based on the command op-code.

The DCE FSW supports the following command performance constraints:

- The FSW is required to process command packet data from the CS at a rate no faster than 1 command packet per second. The DCE FSW may process command packets faster, but all command execution and housekeeping packet traffic must complete within one second of the command packet being received.

- The DCE FSW resets the DCE when it has not received a valid command from the CS in the last 10 seconds. This assumes the CS commanded the DCE FSW to enable watchdog timer resets.

- A command packet may be preceded by up to 512 32-bit words of upload data. A command packet consists of 32-bit words that may be sent in any order, provided that the command word containing the opcode is transmitted last.

All commands are sent via a command link to the DCE. On the CS side, a FIFO is in place to buffer up commands to the DCE. On the DCE side, each 32-bit word in the FIFO is transferred into a set of four 8-bit registers. The DCE reads these registers to form a 32-bit command word.

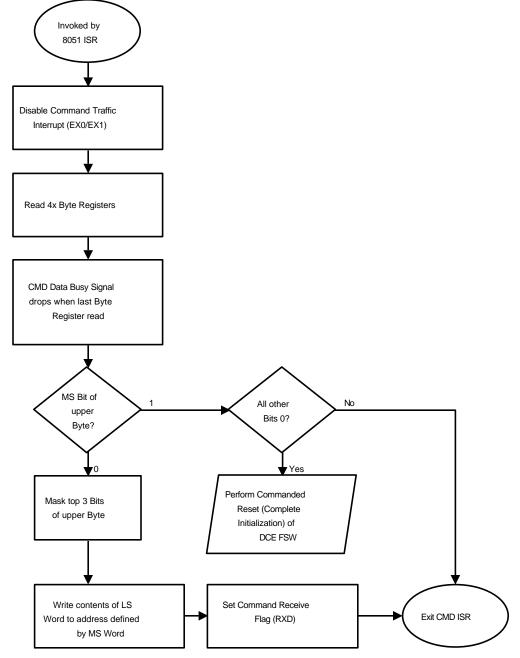

When 32-bits of command data arrives from the CS, the DCE hardware generates an interrupt. The FSW reacts to the interrupt and processes the 32-bit command word. The DCE FSW uses the most significant 16-bits of the command word to identify the type of data contained in the least significant 16-bits of the command word.

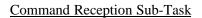

This CSC consists of an interrupt service routine to handle the receipt of 32-bit command words arriving at the command interface. It also contains a task for processing the commands entering the system. It does not, however, include all of the command functions. Command functions are allocated to the various CSCs based on functionality. A special Support Functions CSC exists that contains the command functions that do not map well to one of the other CSCs.

# 3.2.3 Housekeeping Collection and Reporting CSC

The main insight into the operations of the FUV Detector Subsystem comes through the housekeeping data. To gain the required visibility into the detector operations, all key detector parameters are identified and placed into the housekeeping data stream to the CS. Within the constraints of the engineering telemetry bandwidth and in accordance with the FUV ICD document, each key parameter is output in housekeeping at a rate sufficient to determine the health of the FUV detector and to perform a trend analysis on that parameter.

The DCE FSW provides the ability to collect, format, and output the engineering data necessary to achieve the scientific objectives of the FUV Detector Subsystem and to maintain the health and safety of the detector. The FSW responds with a housekeeping packet every time it receives a command from the CS.

In general, a housekeeping packet includes talk backs for all commanded settings; monitors for various temperature, voltage, current, and other sensors; command packet counters; photon event counters; pulse-height histogram data; self-test and diagnostic information; and status flags. Memory download data is sent out as a separate packet of data through the housekeeping channel and is not considered part of the Housekeeping CSC.

The DCE FSW supports the following housekeeping performance constraints:

- The FSW outputs engineering telemetry data to the CS at the rate of 512 32-bit housekeeping words per command response.

- Housekeeping may also include 512 32-bit memory download words transmitted in response to a memory download command from the CS.

The housekeeping interface between the DCE FSW and the CS is similar to the commanding interface. The DCE uses four 8-bit registers that serially shift data into the housekeeping FIFO in the CS. The DCE FSW writes each 32-bit housekeeping word to the housekeeping registers and the hardware takes care of shifting out the data. The FIFO on the CS side takes care of buffering up the housekeeping data for processing by the CS FSW.

This CSC includes a task that outputs the latest housekeeping data to the housekeeping interface. It also includes the commands required to set memory monitor addresses in the DCE FSW. The detailed description of the housekeeping data format is documented in Appendix D of the FUV ICD.

# 3.2.4 Current Limit Checking CSC

The DCE FSW is capable of collecting and monitoring key housekeeping data items for each of the identified critical FUV detector components. Key detector parameters are monitored at a rate that is sufficient to allow DCE FSW to be capable of performing predetermined corrective actions when a safety violation is discovered.

Most monitors are simply reported in housekeeping with no limit checking being performed by the DCE FSW. Some monitors are deemed critical, like high-voltage current, and are checked often by the DCE FSW. Other monitors, like door current, are also checked but less frequently (e.g. once a second in support of door operations). The DCE FSW is responsible for checking these critical monitors for out-of-limit conditions and taking corrective action.

If a current limit or the auxiliary power limit is violated, the DCE FSW turns off high-voltage power along with auxiliary power. It also puts all controls into a safe configuration. The limit values used by the DCE FSW can be modified either directly via DCE commands or by changing patchable constants.

This CSC includes a task to perform the periodic monitoring of critical detector limits. It also contains the command functions to change limit values and enable/disable limit checking.

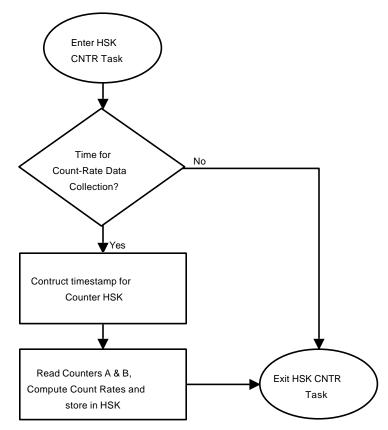

# 3.2.5 Global Rate Protection CSC

The DCE FSW is capable of performing global event rate monitoring of the FUV detector. Global rate protection is implemented to protect the detector from an overlight condition. The FUV hardware has three types of counters: front end counters (FECA & FECB), digitized event counters (DECA & DECB), and science data counters (SDC1 & SDC2). For a complete description of these counters, reference the FUV ICD.

Global rate protection only looks at FEC counter value. The FEC counts are accessible to the DCE FSW via the hardware referred to as Counters A & B. Counters A & B are read on a periodic basis and compared against onboard values. If the either counter exceeds its maximum value, high-voltage is commanded to HV LOW. The threshold values and interval values for global rate protection can be changed on command.

This CSC includes a task that periodically performs global rate protection. The task is invoked once per second. It also includes the command functions to customize the count rate protection scheme, which include changing the threshold value and persistence value.

# 3.2.6 Detector Control CSC

The DCE FSW is capable of controlling the FUV detector electronics. The FUV detector consists of two detector segments named A and B. To support the goal of maintaining optimum detector performance over the life of the instrument, the DCE FSW provides the ability to configure each detector segment along with its associated detector interface electronics on command by the user.

The DCE FSW provides the capability to setup each of the detector segments and their associated interfaces. To aid in maintaining optimum FUV detector performance, the DCE FSW provides the ability to issue instructions to select detector gains, offsets, thresholds, and any other variable detector parameters.

Control of the FUV detector segments falls into one of two categories: detector setup and high-voltage ramping. Detector setup refers to activities that must occur prior to ramping up of the high-voltage. High-voltage ramping refers to the activities required to bring the FUV detector up to its operating voltage. The following three subsections address the topics of detector setup, high-voltage ramping and high-voltage status flags.

This CSC includes a task that controls and monitors the ramp up process. It includes the command functions to configure the digitizers, voltage settings and stim pulses. It also includes the command functions that initiate high-voltage ramp up and set the maximum allowable voltage level.

### 3.2.6.1 Detector Setup

The FSW provides a means of initializing the detectors for operational use. The flight software can configure the digitizers, high-voltage and stim pulses in preparation for exposures. The digitizer setup commands tune the way the digitizers process photon events. The voltage setup commands set values used by the high-voltage ramping process. The stim pulse commands control the stim pulse hardware. The following is a list of the types of detector setup commands processed by the DCE FSW.

Digitizer setup commands

- establish threshold and performance trim settings

- tune image position settings (offset and stretch, both segments, both axis)

Voltage setup commands

- set the low voltage value (voltage to go to when transitioning from high to low voltage, or when a count rate protection limit is exceeded)

- set the nominal high voltage value (voltage level at which to stop ramping HV)

- set the HV ramp rate (pause between HV ramp steps)

- set the maximum voltage level enforced by the hardware (this hardware protection does not let the FSW command high-voltage higher than the maximum limit)

Stim Pulse commands

- turn on and off the stim pulses

- set the rate at which stim pulse events occur

### 3.2.6.2 High-Voltage (HV) Ramping

High-voltage ramp up increases the MCP voltage on the detector in small increments starting at the current high-voltage level (LOW, NOM, NOMA, or NOMB) until it reaches the commanded nominal high-voltage value (NOM, NOMA or NOMB). The high-voltage ramp up process can be tailored using the detector voltage setup commands described above. The HV ramp rate is used to pause for a set amount of time between successive commands to increase the high-voltage. The DCE FSW supports a HV ramp command that starts the ramping process from the current high-voltage level and raises it to the specified level.

### 3.2.6.3 High-Voltage (HV) State Bits

The HV state bits are designed to reflect the expected state of the high voltage. This means that the DCE FSW updates the HV state bits whenever it configures the hardware to a new high-voltage state. Reconfiguration of the HV hardware occurs because a command was received from the CS to change the HV state, or because an event occurred within the DCE FSW (e.g. current limit violation) that causes the FSW to change the HV state autonomously.

The DCE FSW changes the HV state bits under the following conditions:

- a voltage set command (LFHVSET or LFHSTATE) was received from the CS

- a power command (LFHVPWR) was received from the CS

- the DCE FSW took autonomous action to change the HV state (a count rate violation puts HV in LOW, NOMA or NOMB depending on the violation; a limit violation turns off the HV; a DCE reset turns off the HV)

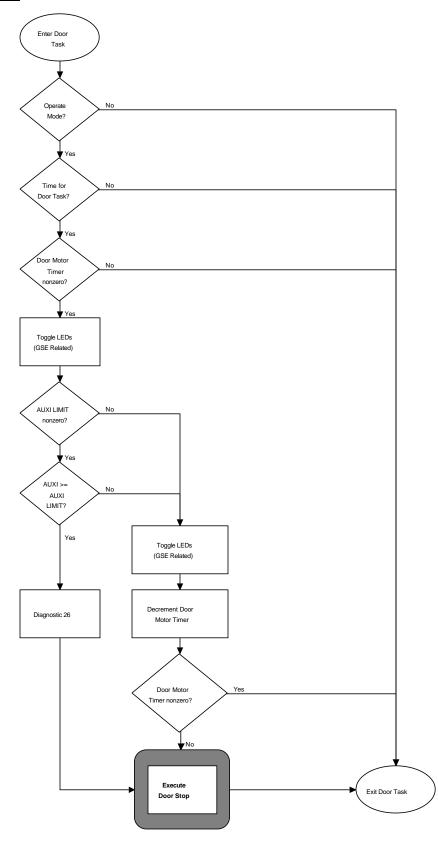

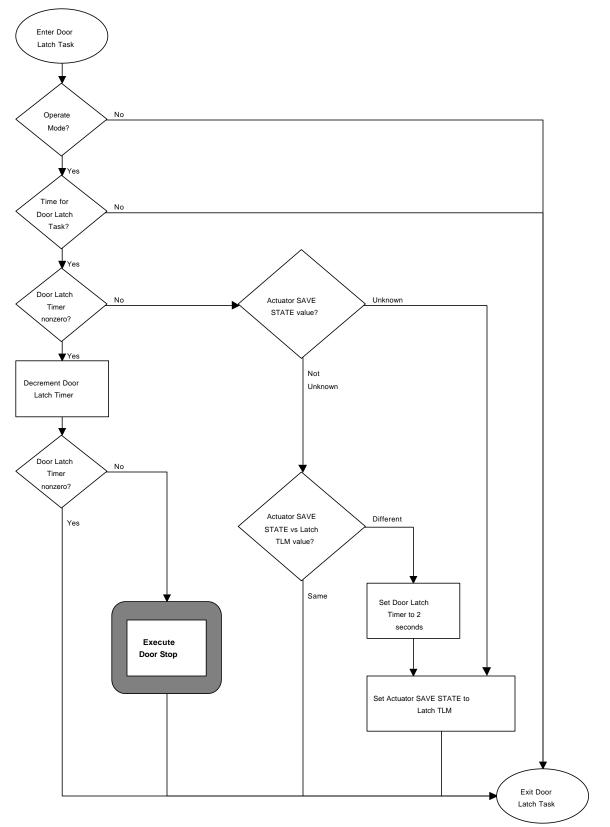

## 3.2.7 Door Control CSC

Reliable and safe configuration of the FUV detector door is a critical factor in supporting the capability of the detector to meet its scientific performance requirements. The door must be open for the FUV detector to perform useful science. The DCE FSW performs the functions necessary to configure and position the door using the support electronics.

Door control falls into two categories: motor control and actuator control. Motor control commands allow the door to be moved using the door motor. This is the primary method of moving the door mechanism. Actuator control commands allow the door to be moved in the event the door motor fails. The actuator is a limited life mechanism and can be reset using the door motor.

Motor control commands

- turn on aux power supply

- start a timer to guarantee that the door move completes within a certain time

- enable commanding of the door motor via a timer (another level of protection)

- set direction of the move

- turn on motor power

- enable door end switch override to allow the door to be reset after actuator use

Actuator control comands

- turn on aux power supply

- start a timer to guarantee that the actuator activation completes within a certain time

- select one of two actuator windings

- turn on actuator power

Since the FUV door may only be opened when the COS instrument is in a vacuum, it is critical that the door not inadvertently open. The door has interlocks to prevent inadvertent powering of the door motor or actuators. Some of these interlocks are in hardware while others are in software. The DCE FSW requires at least two separate command packets to move the door. Additionally, the DCE FSW requires that all door and actuator moves be completed within 3 minutes. If the command timer expires, a *door stop* is performed to put the door in a safe state. The state of the DCE that constitutes a *door stop* is covered in the detailed design portion of this document.

The FSW does not monitor door moves since the door hardware uses optical switches to determine when a move is done. The FSW monitors the aux power current limit when a door move is in progress. Nominally, the current limit

protection software monitors this limit, however, the door control software also monitors it during a door move. If the door control software detects a limit break, a *door stop* is performed.

There are a number of events that can result in a *door stop* occurring. A *door stop* command, door timeout, or DCE reset causes any door move to stop. The FSW stops the door motion by reverting to its initialization state: door and actuator power off, and door commands disabled. The door latch opening or closing also causes the FSW to perform a *door stop*.

This CSC includes a task that monitors the current draw of the door and the door latch position. The CSC also includes the command functions that initiate moving the door, turn on and off the aux power supply, and initiate user of the actuator.

# 3.2.8 Background Monitoring CSC

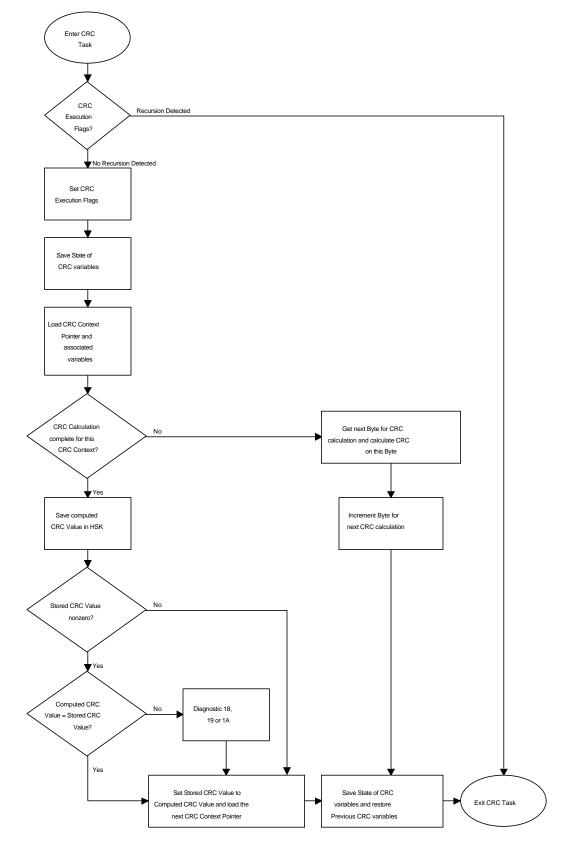

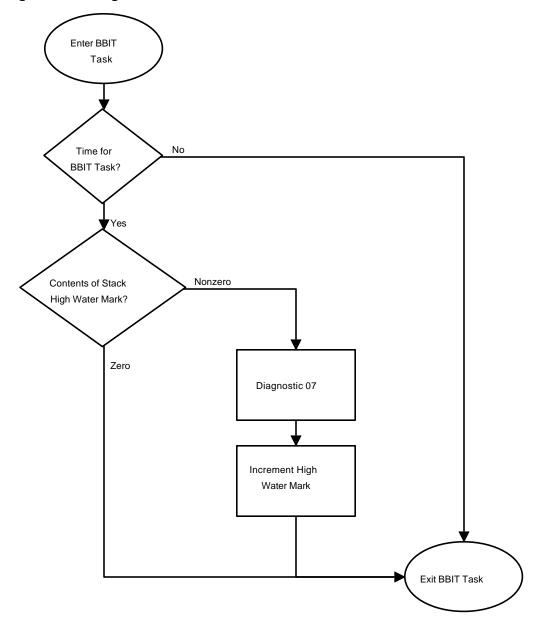

The DCE FSW performs certain self-checks during initialization and during normal operations. The FSW reports any unusual or unexpected conditions as diagnostic messages. The DCE FSW performs two types of background monitoring: CRC checking of memory, and high-water mark monitoring of the stack. The CRC checking is designed to actively look for problems, such as SEUs, in memory. Stack monitoring is intended to track execution of code that causes the stack to grow unexpectedly large.

This CSC includes a task that performs a CRC check on defined memory ranges and a task that performs a background built-in test (BBIT) on the stack to determine its high-water mark. There are no command functions associated with this CSC since background monitoring cannot be disabled.

# 3.2.9 Support Functions CSC

The support functions include all DCE command functions that support DCE operations, but do not conveniently fall into one of the other CSCs. The types of command functions that are considered support functions include: no-op command, memory load and copy commands, jump commands, watchdog timer commands, and reset commands among others.

This CSC includes any command functions used in support of detector operations that do not fall into one of the other CSCs.

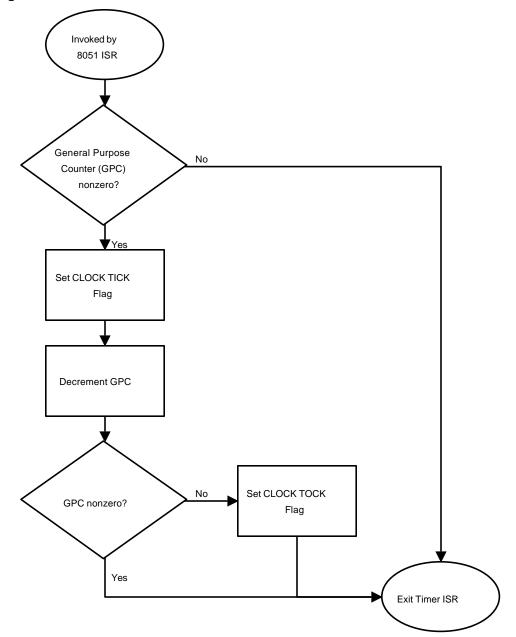

# 3.2.10 Time Management CSC

The DCE provides hardware timers that are used by the DCE FSW to track time. The FSW must be aware of time in order to perform certain time critical tasks.

There is a need for two hardware timers: a timer tick set to 49.152 ticks per second, and a watchdog timer set to 10 seconds. Both timers are programmed during initialization. The watchdog timer must be reset within 10 seconds otherwise a watchdog timer reset occurs.

The timer tick interrupt service routine keeps track of the number of times it is invoked. By doing this, it can maintain software timers. The software timers are used to control the following activities:

- expiration of the door move timer

- expiration of the door latch timer

- collection of Counter A & B data

- invocation of the count rate protection software

- invocation of the high-voltage ramping software

The DCE hardware has a 16MHz clock that is fed into the 8051 microcontroller's timer hardware. The 8051 hardware automatically divides the clock down by 12, which effectively results in a 1.333 MHz clock. The 8051

timer is set to free running 16-bit mode which means that it will rollover (i.e. tick) once every 49.152 milliseconds when its counter overflows. The timer tick calculation is as follows:

1 second / 1,333,333.333 counts \* 65536 counts / 1 tick = 0.049152 seconds/tick = 49.152 msec/tick

This CSC includes the interrupt service routine that manages time for the rest of the DCE FSW.

# 3.3 Control Flow

The control flow section shows how the software components are combined to form the DCE FSW. This section shows the flow of control through the system, and how processing logic is affected by the various events that occur in the system. The System Level Control Flow Diagram is included to graphically show how the DCE FSW works.

The basic design of the software control flow is that of an initialization sequence followed by an infinite processing loop. This control flow originates with a reset event, such as power-on to the DCE. The main software processing loop, called the executive loop, can be interrupted by a hardware signal that directs the 8051 to execute a special sequence of code called an interrupt service routine (ISR). ISRs are designed to execute quickly and terminate, restoring control to the executive loop at the point it was interrupted.

Figure 3.3-1 is the System Level Control Flow Diagram for the DCE flight software.

COS DCE Flight Software Design Document

- This diagram is an idealized version of the Executive Loop with the order of task invocation being approximate. The actual order that tasks are invoked in the executive loop is documented in the detailed design section.

- The Jump Entry Point is the point of entry for the jump command when jumping from Boot to Operate, Operate to Operate, or Boot to Boot.

- The Inspect & Change Task is greyed because the current design does not have this task included in the software. The hooks are left in place just in case the task becomes necessary for test purposes.

Figure 3.3-1. System Level Control Flow Diagram

## 3.4 Data Flow

The data flow section shows how data flows in and out of the DCE FSW. This section is only concerned with data that enters and leaves the flight software. The Context Level Data Flow Diagram is included to graphically show the system level data flows.

The data flow diagram depicts the DCE FSW as a single entity with interfaces to the DCE and CS hardware. The diagram uses three types of symbols to represent the various entities in the system. A circle represents the DCE flight software. Round-cornered boxes represent the DCE interface hardware that is used by the DCE FSW to control and/or status some piece of DCE hardware, or to communicate with the CS. The square-cornered boxes represent the DCE FSW is communicating.

It should be noted that the diagram depicts the flow of data between MON51 test software and the DCE FSW. The flight version of the DCE FSW will not contain MON51 related software, however, the data flow is included here for completeness.

Figure 3.4-1 is the Context Level Data Flow Diagram for the DCE flight software.

Figure 3.4-1. Context Level Data Flow Diagram

## 3.5 Hardware Interfaces

This section describes the hardware interfaces that are external to the DCE flight software. External interfaces refer to the following:

- DCE hardware that the DCE FSW controls and reads status from

- CS hardware that the DCE FSW receives commands from and sends housekeeping data to

External interfaces are represented by the round-cornered boxes depicted in the Context Level Data Flow Diagram shown in Figure 3.4-1. As a point of comparison, internal interfaces refer to the 8051 micro-controller ports and memory mapped I/O address used by the DCE FSW to access the external interfaces. The detailed design section of this document provides a complete description of 8051 ports and memory mapped I/O and how they are used by the FSW.

The external interfaces are dealt with at a high-level. The intent of this section is to describe the type of hardware control and status that the DCE FSW provides. The low-level commanding of the hardware (i.e. which bits in which register to set or clear) is defined in the DCE Hardware-to-Software Interface document.

This section is broken down into two subsections. The first subsection looks at the interfaces between the DCE FSW and the CS, and the second subsection examines the interfaces between the DCE FSW and the DCE hardware. Within those two subsections, all of the external interfaces are described. Each external interface is described in terms of the control provided by the DCE FSW and the status returned by the hardware.

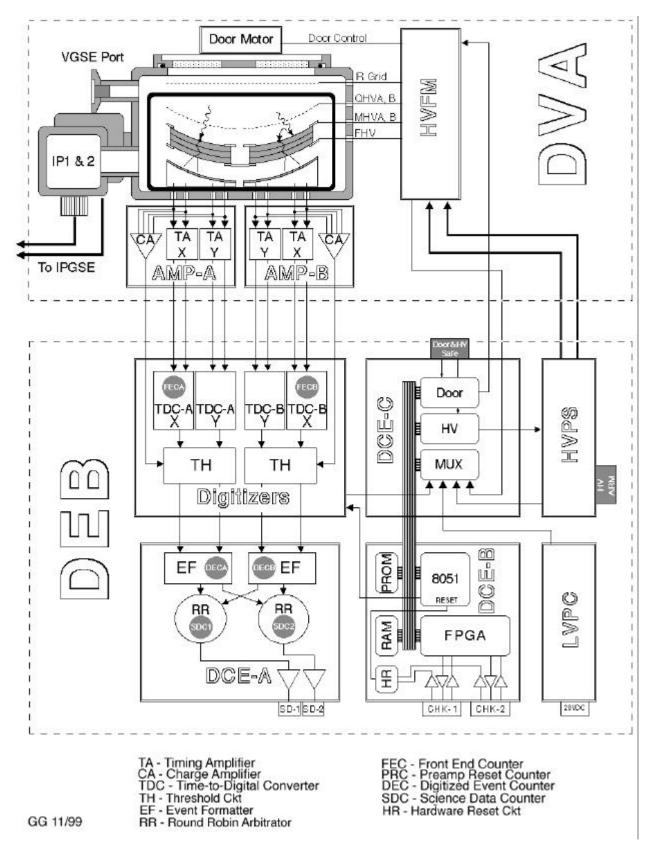

Figure 3.5-1 (shown below) is the FUV Detector Functional Block Diagram. It provides an overview of the FUV detector hardware. It is included here to provide additional information about the hardware that is controlled by the DCE FSW.

Figure 3.5–1. FUV Detector Functional Block Diagram

# 3.5.1 Interfaces Between the CS and DCE FSW

### 3.5.1.1 Command Registers

All DCE commands are sent via a command link from the CS to the DCE. On the CS side, a FIFO is in place to buffer up commands to the DCE. On the DCE side, each 32-bit word in the FIFO is transferred into a set of four 8-bit command registers. The act of reading the last of the 8-bit registers by the DCE FSW clears the "busy" bit and allows the next 32-bit CS FIFO value to be placed into the command registers.

The DCE has two redundant command links, A and B, which are both always active. Either link may be used to command the DCE at any time. The DCE FSW reads one set of command registers to process a command if one is present. If no command is present, it then reads the alternate set of command registers.

### 3.5.1.2 Housekeeping Registers

The housekeeping interface between the DCE and the MEB is similar to the commanding interface. The DCE uses four 8-bit registers that serially shift out data into the housekeeping FIFO in the CS. The DCE FSW writes each 32-bit housekeeping word to the housekeeping registers and the DCE hardware takes care of shifting out the data into the housekeeping FIFO. The FIFO on the CS side takes care of buffering up housekeeping data for processing by the CS FSW.

## 3.5.2 Interfaces Between the DCE FSW and the FUV Hardware

### 3.5.2.1 Control Registers

The DCE FSW controls the high-voltage power supply (HVPS) and the door mechanism by setting and clearing bits in one of two control registers. The control bits that can cause severe degradation to the FUV detector if used incorrectly are allocated to a protected control register that has been equipped with a *lock* bit. The use of the lock bit is described in detail in the DCE Hardware-to-Software Interface document. The remaining control bits that cannot cause damage to the FUV detector have been allocated to an unprotected control register.

#### 3.5.2.1.1 Protected Control Register

The protected control register contains control bits that can cause damage to the FUV detector if used incorrectly. The control bits allocated to this register are as follows:

- *HV power* Turns on/off power to both the grid & MCP.

- Ion pump on/off For GSE use only since ion pumps are not used in orbit.

- PROM/RAM When zero, 8051 uses PROM for executing code. When one, it uses 8K RAM.

- *Door end switch override* When override is enabled, the door auto-stop capability is not in effect. When disabled, the door auto-stop capability turns off power to the door motor.

- Actuator A and B power Turns on/off power to actuators A and B.

- *Door motor power* Turns on/off power to the door motor.

#### 3.5.2.1.2 Unprotected Control Register

The unprotected control register contains control bits that cannot damage the FUV detector. The control bits allocated to this register are as follows:

- *Aux power* Enables/disables auxiliary power for moving the door motor or actuators.

- *Door direction* Sets the direction of a door move.

- *Actuator enable* Enables/disables actuator support circuitry which allows the actuators to be powered. The DCE FSW mirrors the state of actuator enable bit in software for use in processing actuator commands.

## 3.5.2.2 HVPS Digital-to-Analog Converter (DAC)

The DCE FSW uses the High-Voltage Power Supply (HVPS) Digital-to-Analog Converter (DAC) to control the HVPS. The DAC converts a digital value to a high-voltage value in the approximate range of -2000 to -6000 volts at the detector head.

The DCE FSW uses the DAC to command the HVPS to a new voltage level and to set the maximum voltage level. Status information concerning the state of the HVPS is returned to the FSW via the multiplexer (MUX) and Analog-to-Digital Converter (ADC).

## 3.5.2.3 Digitizer 3-Wire Interface

The digitizer is the electronics that interprets photon events. The criterion used to qualify an event can be controlled via commands. The digitizers commands are sent via a synchronous serial link implemented with 8051 port pins. The digitizer returns setting talk-backs as an input to the MUX/ADC. The digitizer is programmed with default values upon power-on reset, and after that, settings are modified only on command.

The DCE FSW uses a 3-wire interface to send commands to the digitizer hardware. The DCE FSW sends values that set event filtering values among other adjustment values for controlling digitizer performance. The FSW sends over digital values that are converted to analog values by the digitizer.

## 3.5.2.4 Serial I/O Port

The serial I/O port is a feature built-in to the 8051 microcontroller. It is used to provide a back door method of communicating with the DCE FSW. Test versions of the DCE FSW might include capabilities to use the serial I/O port for communicating with special COTS test software (MON51).

### 3.5.2.5 Analog-to-Digital Converter (ADC)

An analog-to-digital converter (ADC) converts sensor voltages to digital values that are stored in the housekeeping data area. The sensors can collect temperature, voltage or current information, and hardware talk-back information.

The FSW must use the multiplexer (MUX) to select the appropriate ADC input source and to tell the ADC to perform the conversion. After selecting the desired source and initiating the conversion, the FSW must wait a short time for the input to settle. After waiting the settle time, the FSW reads the ADC converted value and stores it in the appropriate housekeeping location.

Certain ADC inputs (e.g. current limits) must be gathered at a high rate, while all other ADC inputs are read just before the FSW sends out the housekeeping data. The current limit protection software collects current limit information from the ADC and uses it in its protection algorithm.

### 3.5.2.6 Multiplexer (MUX)

As described in the ADC section, the multiplexer is used to select the appropriate input to the analog-to-digital converter. There are a number of possible ADC inputs that can be selected using the MUX.

In addition to selecting ADC inputs by writing to the MUX address, the same address is used to gather status information about the door and high-voltage. The state of the door and high-voltage can be determined by reading the MUX address. It should be noted that the DCE FSW is not reading from the MUX but rather from another latch that has the same address as the MUX. Some of the status bits reflect whether HV and grid have been powered on, and door switches (latched, opened and closed).

### 3.5.2.7 Counters

Counters reflect the number of photon events that have passed through the various stages of the digitizing process. There are several types of counters that count specific types of events. The FUV hardware has three types of counters: front end counters (FECA & FECB), digitized event counters (DECA & DECB), and science data counters (SDC1 & SDC2). For a complete description of these counters, reference the FUV ICD.

Each counter counts only the photon events that meet some criterion specified by the digitizer and its threshold settings. The count rate protection software uses the FEC counters to determine when a global count rate violation has occurred. Each type of counter has an A & B counter that maps to each FUV detector segment.

### 3.5.2.8 Pulse Height Histograms

Pulse Height (PH) Histogram data consists of 128 bins of consecutive 16-bit words. This data represent the total number of photons that were detected and distributed into bins according to their pulse-height as determined by the digitizer hardware. There are two PH Histogram bins: one for MCP Segment A and one for MCP Segment B.

The FSW periodically reads the PH bins and outputs that information to the CS through housekeeping. The act of reading the PH data causes the bins to be reset to zero.

The memory used to store PH data is accessible to both the PH Counter hardware and the 8051. An attempt to simultaneously access the same memory by both the 8051 and the PH Counter hardware could result in corrupted data. The PH Counter hardware design requires the 8051 to assert a PH disable signal while accessing the PH Counter memory and de-assert the signal when done.

### 3.5.2.9 Miscellaneous

There are several external interfaces that are used for GSE purposes only. They are mentioned here for completeness.

- *LEDs* used during testing to verify that something is happening

- *Reset pin* resets the DCE hardware

- External reset link external reset controlled by the CS

# 3.6 Operating Modes

This section examines the two DCE FSW operating modes: Boot and Operate. It describes the functionality the operating modes provide and how the user transitions from one mode to another. The concept of Boot and Operate modes is borrowed directly from the CS flight software design.

The DCE FSW is composed of three related software executables known as the *Boot code image*, *Upper Operate code image* and the *Lower Operate code image*. All three executables are built from the same source code files. This means that the same executable code is built into all images, however, only certain functionality is available depending on the operating mode. The software determines the operating mode based on the area of memory from which the code is executing. For example, if the code is executing from PROM address space, the mode is Boot. If the code is executing from 32K RAM, the mode is Operate.

The Boot code image is burned into PROM and cannot be changed once the COS instrument is on-orbit. The Operate code image is stored in the EEPROM within the CS and can be updated over the life of the COS instrument. The following sections describe each DCE FSW operating mode in detail.

# 3.6.1 Boot Mode

The DCE embedded processor begins execution of the Boot flight software contained in PROM whenever power is applied to the FUV Detector Subsystem or when a reset occurs. The primary purpose of the Boot software is to provide a robust, non-volatile code image from which to load the Operate code images into RAM. Once the DCE is in Boot mode, the ground can then send commands to put the FUV Detector Subsystem into an operational state.

The Boot code provides enough capabilities to upload an Operate code image and transfer microprocessor control to the Operate code. This allows the Operate code image to be actively managed on the ground and new versions to be uploaded to the COS instrument. The Boot code also allows memory tests to be performed on the Upper Operate and Lower Operate code areas in 32K RAM area since Boot runs out of PROM.

The Boot code provides a subset of the capabilities found in the Operate code. The following is a list of Boot code capabilities:

- Perform initialization functions, including reset tests and memory initialization.

- Command reception and processing

- Housekeeping data reporting including memory monitors

- Memory uploads from the CS into DCE RAM

- Memory dumps from DCE memory to the CS

- Begin execution of the Operate code image

- Processing of a subset of DCE commands (but *no* HV, door or digitizer commands)

- Background CRC checking and stack monitoring

Since Boot does not support any HV, door or digitizer commanding, there is no need for count rate protection or current limit protection capabilities.

For a list of all commands valid in Boot mode see the DCE Command section of this document.

### 3.6.2 Operate Mode

Operate mode is entered after a DCE Operate code image has been loaded into DCE memory and the ground has issued the jump-to-operate command. After receiving the jump-to-operate command, the Boot code transfers control to the specified Operate code image. Up to two Operate images can be stored in DCE memory at the same time: one in the lower code area (LCA) and one in the upper code area (UCA).

The Operate code provides a superset of FUV detector control capabilities. The following is a list of Operate code capabilities:

- Command reception and processing

- Housekeeping data reporting including memory monitors

- Memory uploads from the CS into DCE RAM

- Memory dumps from DCE memory to the CS

- Begin execution of the other Operate code image

- Processing of all DCE commands including HV, door and digitizer commands

- Ramp detector high-voltage

- Current limit protection

- Count rate protection

- Move the door mechanism

- Background CRC checking and stack monitoring

For a list of all commands valid in Operate mode see the DCE Command section of this document.

# 3.6.3 Mode Transitions

As described above, Boot code begins executing as the result of power being applied to the FUV detector electronics or due to a microprocessor reset. Once in Boot mode, the ground commands the CS to copy the DCE Operate image to the DCE. Once the image is successfully copied, the ground issues a command to transfer control to the Operate code. This is the standard process for transitioning between Boot and Operate modes.

Boot mode can be entered under the following conditions:

- a power-on reset occurs

- a watchdog timer reset occurs while in Boot mode (because the watchdog timer was not stroked)

- a reset command was received and processed by the Boot mode software

- a watchdog timer reset occurs while in Operate mode

- a reset command was received and processed by the Boot mode software

Operate mode can be entered under the following conditions:

- a jump-to-Operate command was received and processed while executing in Boot mode

- a jump-to-Operate command was received and processed while executing UCA Operate code

- a jump-to-Operate command was received and processed while executing LCA Operate code

The following figure shows all the possible means of transferring between Boot and Operate modes.

Figure 3.6-1. DCE Flight Software O perating M odes

# 4 DETAILED DESIGN

## 4.1 Design Approach

This section describes the overall software design approach to the DCE FSW. There are several factors that impact the way in which the DCE FSW is designed. This section examines these factors and attempts to describe how they influence the design.

# 4.1.1 Reuse from Previous Missions

The most influential factor is the reuse of software from previous missions. Previous missions that have used the same detector subsystem as the COS FUV detector include Far Ultraviolet Spectroscopic Explorer (FUSE) and Galaxy Explorer (GALEX). The reuse of software from one or both of these projects has a profound impact on how the COS DCE FSW is designed.

The lineage of the DCE flight software starts with FUSE and is followed by GALEX and COS. The bulk of the COS software design is based on the FUSE code.

Since the DCE FSW is relying on heavy design and code reuse from previous missions using the same detector subsystem, the detailed design reflects this reuse. Each subsection of the Software Architecture section includes a reuse description that details the level of reuse we expect to achieve. It also describes any changes or modifications we expect to make for COS.

# 4.1.2 Memory Utilization and Commanding

### 4.1.2.1 Memory and Op-Code Usage

Data structures are in fixed locations in memory and generally do not change from one version to the next. Command op-codes are dedicated to a specific function and are never reused. Although some commands may be retired and supporting code removed, the command op-code associated with that command function is never reused.

### 4.1.2.2 Commandable "Energy"

Commands for the HV and the door mechanism are considered *special* because they have the potential to severely degrade the performance of the detector. As special commands, the "energy" of the HV or door is not increased except when enabled by a separate software interlock. The energy level can be reduced, however, regardless of the state of the software interlock. This means that commands to turn *off* the door power do not require an "enable" flag to execute the command. A command to turn *on* the door power, however, does not turn on power unless a "Door Enable" command is issued first.

The general concept is that of a subsystem "energy level". A subsystem with power applied to it has a higher energy level than a subsystem that is powered off. For example, detector MCPs running at nominal HV have a higher energy level than detector MCPs running at low HV. Increasing HV from low to nominal requires software protections while reducing HV from nominal to low does not.

# 4.1.3 Boot and Operate Software Designs

### 4.1.3.1 Equivalent Executable Images

To maximize FUSE code reuse, the COS DCE Boot and Operate images are logically equivalent. The DCE FSW is designed such that the Boot and Operate images use the exact same source code files. Since the images run out of different areas in DCE memory, the linker produces executable images with addressing relative to the target memory

area. This means the images are logically equivalent, however, not identical. Figure 4.1-1 below shows how the Boot and Operate code images are located in DCE memory. For a detailed view of the contents of DCE memory, see the DCE memory map described in section 4.4.2.3.

The code is constructed such that a single set of source code can be used to build both Boot and Operate images. At the beginning of any task or command functions that is *not* executed while in Boot mode, code exists to check the current operating state of the FSW. If the software is executing out of the PROM address range, the DCE FSW does not execute the function or task associated with Boot mode. Should the DCE FSW receive a command while in Boot mode that is not a valid Boot mode command, it issues a diagnostic stating that an invalid Boot mode command was received.

The Boot code image also contains a *data area* that consists of a GSE Operate Test Image. This test image is intended for use only during GSE testing and is located with Boot in PROM for easy copying to RAM.

Figure 4.1–1. Code Image Location in DCE M emory

#### 4.1.3.2 Common Variable Space

Both Boot and Operate use the same space in RAM to store variable information. In addition, Operate images that exist in the upper and lower code area also share the same RAM space for variables. Any software variables that are common to Boot and Operate are overwritten whenever a system reset occurs, or when the ground commands the DCE to jump to Operate. This means that the state of software variables is not preserved in the event of a reset.

# 4.2 Software Architecture

Software architecture deals with the physical grouping of code versus the logical groupings called out in the top-level design section. The top-level design looks at the functionality of the DCE FSW from a logical perspective while the detailed design organizes processing logic into physical components.

This section addresses the physical software components that make up the DCE FSW. In the DCE FSW there are five major software component types: initialization code, an executive loop, interrupt service routines, tasks, and command functions. Each type of component is discussed in the following sections. Before looking at the major software components individually, a discussion of the operating system is necessary. The operating system overview describes how these software components are used together.

# 4.2.1 Operating System

The DCE flight software does not use a commercial off-the-shelf (COTS) operating system (OS). The operating system is built from the ground up using a simple design. The DCE FSW operating system consists of an executive loop that invokes a series of functions in a round-robin fashion along with interrupts that provide pre-emptive processing. The functions invoked by the executive loop are called *tasks*. Each task provides a unique set of functionality to the DCE FSW. Some of the tasks that make up the flight software include the command handler task, high-voltage ramping task, count rate protection task, among others. Each of these tasks is described in greater detail in following sections. The concept of tasks in the context of the DCE FSW is described in greater detail later in the document.

### 4.2.1.1 Overview

The easiest way to describe how the DCE FSW operating system works is to compare it to another operating system. Since the HST program is familiar with the operating system used by the Control Section Flight Software, it will be used as the point of comparison. The CS FSW uses the iRMK 1.3 commercial off-the-shelf operating system produced by the Intel Corporation. The iRMK operating system (or iRMK kernel as it is more commonly referred) handles all aspects of task switching and control.

Like the DCE OS, the iRMK kernel uses interrupts to provide pre-emptive processing. *Unlike* the DCE OS, the iRMK kernel allows the user to assign priorities to each task in the system. iRMK automatically determines when the highest priority task in the system is ready to run, switches it in, and starts executing it. It saves the state of the current task before switching in the next task. Since iRMK completely manages the switching of tasks, the developer does not need to deal with saving the task state. iRMK does that automatically.

In the DCE OS, there is no task priority concept. All tasks run at the same priority level. The round-robin nature of the executive loop means that all tasks are invoked in turn and the order cannot be dynamically altered. The following section details the concept of tasks in the DCE FSW and how they are constructed.

Due to the lack of task prioritization in the DCE OS, timing is less uniform than might be found with the iRMK OS used in the CS. This means the DCE does not provide uniform timing of certain events. An example of this is the execution of a command that takes a long time to complete (e.g. memory dump). A memory dump can impact the timing of other functions like high-voltage ramping. Performing a memory dump while ramping high-voltage might mean the DCE cannot maintain the 100 millisecond timing granularity of HV ramping.

It is worth mentioning, that performing a memory dump while ramping high-voltage will not be performed operationally. Based on the speed at which the DCE FSW executes as well as how the DCE is commanded in an operational environment, this timing non-uniformity is not considered a problem.

For a list of timing issues that result from the DCE OS design, see section 4.2.8.2.1, *Timing Considerations*, later in this document.

## 4.2.1.2 Tasks

Tasks in the DCE flight software are constructed differently than tasks in the CS flight software. As described in the operating system overview section above, tasks are invoked in round-robin fashion by the executive loop. The executive loop does not manage the switching in and out of tasks, which would take care of retaining a task's state information between invocations. The tasks, therefore, must be capable of retaining their own state information.

To ensure timely progress through the executive loop, tasks must execute quickly and return control to the executive loop. To accomplish this, each task runs to completion, however, it performs only a portion of its total work each time it is invoked. For example, the task that calculates a CRC only calculates one byte of CRC each time it is invoked. The task must be invoked many times in order to calculate the CRC for an entire range of memory. Each time a task is invoked it:

- checks its current state

- determines if its state should change based on the presence of certain conditions (i.e. events)

- performs the work associated with that state

- saves it state and returns control to the executive loop

This means that tasks in the DCE FSW must be constructed as state machines. Each task must manage its own state, keep track of which events have occurred, and determine whether its state should change as a result of a particular event occurring. Each task is designed to record its current state in a data structure and change its state in response to events. Events include things like the arrival of a command word, a one-second timer tick, or a timeout flag. Each task responds to a unique set of events. A complete description of each task, its states, and the events that drive it are covered in detail in the following sections.

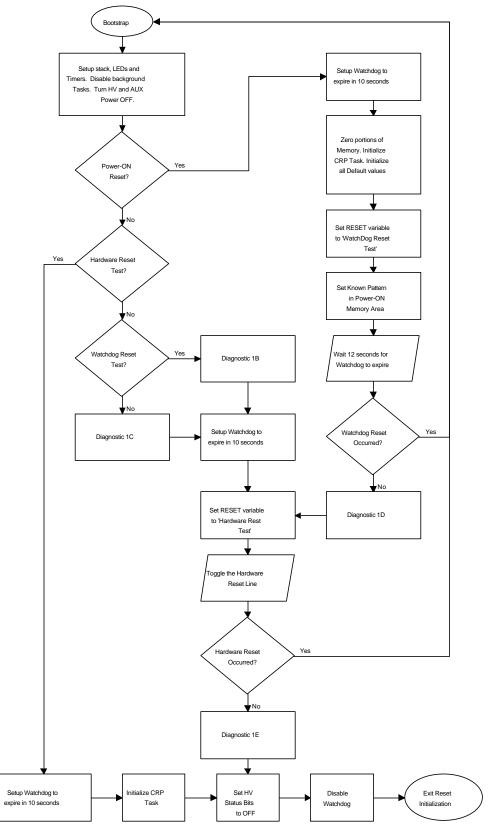

### 4.2.2 Resets and Initialization

The DCE can be reset for a variety of reasons. A reset occurs whenever power is applied to the DCE, or whenever the watchdog timer has not been stroked quickly enough. Each of these resets causes the DCE FSW to start executing from its PROM. This section examines the resets that can occur in the system and how the DCE FSW initializes itself as a result of the various resets.

FUV detector initialization consists of the steps the DCE FSW must go through to properly setup its operating environment. Initialization steps include configuring the various pieces of DCE hardware, initializing global memory areas and starting execution of the various tasks in the system. This section covers the DCE FSW requirements that deal with resetting the system and causing the DCE FSW to re-initialize.

Figure 4.2-1 shows the logic flow associated with resets.

Figure 4.2-1. DCE Resets

#### 4.2.2.1 Power-On Reset

A power-on reset (POR) is treated as if the hardware has just been powered on. While this kind of reset is intended to be used only during an actual power-on event, it is also a commandable event that forces the DCE into a default, known state. A power-on reset causes a complete initialization of the software to occur. This is described in detail in the *Complete Initialization Sequence* found in section 4.2.2.4.1.

Interrupts are enabled during a POR, allowing the Command Traffic ISR to process incoming commands even before the Command Handler Task is ready to check the command buffer. The POR purposefully does not write to memory addresses above 0x8800 in order to preserve the state of that memory. During initialization, the watchdog reset and hardware resets are tested.

### 4.2.2.2 Watchdog Reset

A watchdog reset occurs when the watchdog timer has not been "stroked" (i.e. reset) often enough. If the watchdog count down timer reaches zero before being reset, a watchdog timer reset occurs. This type of reset can be due to a single event upset (SEU), a coding error, or some spurious event. Just like the POR, a watchdog timer reset can be commanded from the ground.

This is a catchall-type reset that is named for its most likely cause: the 8051 built-in watchdog reset timer, which can cause the 8051 to jump to its reset vector. This type of reset assumes that power had been previously applied to the DCE. A watchdog reset causes a minimal initialization of the software to occur. This is described in detail in the *Minimal Initialization Sequence* found in section 4.2.2.4.2.

#### 4.2.2.3 Commanded Resets

A commanded reset occurs as a result of a reset command being sent to the DCE FSW from the CS. There are four possible ways to command the DCE FSW to reset the DCE. Two of the commands result in complete reset of the DCE FSW, and the other two result in a minimal initialization. The four ways to command DCE reset include:

- The CS can reset the DCE by toggling the DCE hardware reset line. This does not result in a command being sent to the DCE FSW. This reset command results in the DCE FSW executing its minimal initialization sequence.

- The CS sends an Initiate Watchdog Reset command to the DCE. This reset command results in the DCE FSW executing a minimal initialization sequence.

- The CS sends a single command word that contains the value 0x80000000. This reset command results in the DCE FSW executing a complete initialization sequence.

- The CS sends an Initiate Power-On Reset command to the DCE. This reset command results in the DCE FSW executing a complete initialization sequence. (NOTE: The DCE forces the complete initialization sequence to run by scrambling the *known pattern* in memory to make it appear as if a powered up of the DCE occurred.)

| Source of Reset                                                                     | Initialization Sequence Executed by FSW |

|-------------------------------------------------------------------------------------|-----------------------------------------|

| Power-on Reset: power is applied to the DCE hardware                                | Complete Initialization Sequence        |

| Watchdog Reset: Watchdog timer expires                                              | Minimal Initialization Sequence         |

| <i>Commanded Reset #1</i> : CS sends a command to perform a complete initialization | Complete Initialization Sequence        |

| (aka Initiate Power-On Reset command)                                               |                                         |

| <i>Commanded Reset #2</i> : CS sends a command word containing 0x80000000           | Complete Initialization Sequence        |

| Commanded Reset #3: CS toggles DCE hardware reset line                              | Minimal Initialization Sequence         |

| <i>Commanded Reset #4</i> : CS sends a command to perform a minimal initialization  | Minimal Initialization Sequence         |

| (aka Initiate Watchdog Reset command)                                               |                                         |

#### 4.2.2.3.1 Reset Summary Table

### 4.2.2.4 Initialization

The DCE FSW initializes itself after any reset. The initialization code can distinguish between a POR and any other reset in order to determine how much internal memory to initialize. After a power-on reset, the DCE FSW initializes its memory to a known state by zeroing certain areas of RAM. After any other type of reset, the memory is preserved so that evidence of activity prior to the reset can be analyzed to determine the cause of the reset.

Some initialization is required after any reset to ensure FSW control flow is fully deterministic. This means that all variables needed to properly operate the FSW are initialized to avoid a continuous reset situation. To ensure a continuous reset situation can never hang the DCE FSW, a watchdog reset counter forces a POR after 255 reset events have occurred.

The DCE FSW uses one of two initialization sequences (complete or minimal) depending on the type of reset that occurred. The two initialization sequences are described in more detail in the following subsections.

#### 4.2.2.4.1 Complete Initialization Sequence

A complete initialization sequence is performed in response to a power-on reset occurring, or when the DCE FSW is commanded to perform a complete reset. The following initialization steps are performed:

- Setup the stack.

- Setup the LEDs.

- Disable background tasks.

- Setup the timers.

- Execute the *DCE Safe Controls* procedure (turn off HV power, enable PROMs, disable door end switch override, turn off actuator A & B power, turn off door motor power, set door direction to STOP, turn off auxiliary power, and disable actuator circuitry).

- Configure the watchdog timer to expire in 10 seconds.

- Clear internal registers.

- Initialize 8K RAM.

- Set known pattern in memory to show that we have been powered up and that we performed the complete initialization sequence.

- Zero variables in 32K RAM.

- Initialize all default values including HV Ramping variables, Current Limit Protection variables, and Count Rate Protection variables.

- Initialize the housekeeping buffer to all zeroes.

- Configure digitizers with default values (this turns off the STIM generator).

- Set reset variable to *watchdog reset test*.

- Setup for background CRC calculations.